Journal of Science and Technology Research

Journal homepage: www.nipesjournals.org.ng

## Performance Analysis of Nanoscale Double Gate Ge and GaSb finFETs

## N. M. Shehu\*, M. H. Ali, G. Babaji

Department of Physics, Bayero University, Kano, Nigeria \*<u>nmshehu.phy@buk.edu.ng Tel: +2348038860203</u>

| Article Information                                                                                                        | Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Article history:<br>Received 12 May 2023<br>Revised 09 June 2023<br>Accepted 09 June 2023<br>Available online 13 June 2023 | This paper explores the performance characteristics of Germanium<br>(Ge) and Gallium Antimonide (GaSb) as potential channel<br>materials for finFET devices. The analysis focuses on key factors<br>such as transconductance, on-current and short channel effects<br>(SCEs) using simulations conducted in the Padre Simulator<br>environment. The results reveal that GaSb-finFET exhibits superior<br>transconductance and on-current as well as reduced short channel |

| https://doi.org/10.5281/zenodo.8033886                                                                                     | effects; drain induced barrier lowering (DIBL) and threshold<br>voltage roll-off compared to Ge-finFET. However, Ge-finFET<br>exhibits better characteristics in terms of subthreshold swing (SS)                                                                                                                                                                                                                                                                         |

| <b>Keywords:</b> GaSb-finFET, Ge-FinFET,<br>Transconductance, Channel material,<br>SCEs                                    | These findings are particularly important in application where<br>faster switching capabilities are required.                                                                                                                                                                                                                                                                                                                                                             |

### **1. Introduction**

As we continue to reduce the size of the conventional MOSFETs, achieving excellent performance in semiconductor devices has become more difficult. There will be difficulties if we continue to scale down MOSFETs in the nanoscale regime because of negative effects such as increase in leakage current, drain induced barrier lowering (DIBL), voltage threshold variation and velocity saturation[1][2]. These negative effects are called short channel effects (SCEs).To mitigate the above mentioned effects, it is believed that an alternate structure, such as the Double Gate FinFET (DG-FinFET), can be used to solve the scaling issues, particularly with regard to the device's short channel performance and scalability of nanoscale[3]. The recent focus on FinFET research is due to their many well-known benefits, such as decreased short channel effects[4].

Several studies have been conducted on the short channel effects in fin Field Effect transistors (finFETs). Veshala *et.al* in [5] carried out a research which led to the suppression of leakage current and control of threshold voltage roll-off. Optimization of high performance bulk finFET has been done by researchers in[6]. It has been discovered that the bulk FinFET with bottom spacer can be tuned to outperform all other FinFETs. To improve short channel performance of a finFET another research by[7] has been conducted. The authors reported reduced short channel effects. The impact of downscaling of nano-channel dimensions of Indium Arsenide Fin Feld Effect Transistor (InAs-FinFET) on electrical characteristics of the transistor has been studied in[8]. The authors obtained optimal dimensional parameters' values at scaling factor, K=0.125. In [9], the influence of fin height and width of an n-finFET has been extensively studied. It was proved by the authors that the optimized fin height lies between 50-60 nm.

They also found that the threshold voltage shift by quantum confinement has a steep increase as fin width shrinks to 4 nm. Impact of high-k gate dielectrics on the short channel effects has been studied in[10]. They showed that HfO<sub>2</sub> can be considered as a promising candidate that may be used for nanoscale low power applications. Various electrical characteristics of DG finFET have been analyzed at 45 nm by [11]. The authors used different kinds of dielectric materials in search of the better one. They found that TiO<sub>2</sub> enhanced device functionality, improves gate control over the channel, decreases effective leakage current, and provides high amplification values. In [12] the authors studied short channel effects for Silicon (Si), Gallium Arsenide (GaAs), Indium Arsenide (InAs) and Indium Phosphide(InP) as channel materials in nanoscale MOSFET. The authors were able to show that InSb was the best to be used as channel material.

Study of short channel effects for Si, GaSb, GaAs and GaN channel materials has been carried out by [13]. The authors proved that GaN was the worst in terms of immunity against short channel effects. Comparative performance was carried out by [14] between Silicon (Si) and Gallium Nitride (GaN) as channel materials in finFET. GaN was found to have higher performance at higher voltages and higher temperature than Si. However, no comparative analysis has been conducted on the resistance of Ge and GaSb to short channel effects (SCEs) to determine one which is more immune to SCEs that can be a potential channel material in finFET.

The aim of this study is to evaluate the performance of Ge and GaSb channel materials in finFETs, and to identify the material that exhibits superior performance. The study considers various important parameters such as short channel effects, including drain induced barrier lowering (DIBL), sub-threshold swing (SS), and threshold voltage roll-off, as well as drive (on-current) and transconductance. To accomplish this, simulations are conducted on both Ge and GaSb materials in finFETs.

# 2.0. Methodology 2.1. Device Structure

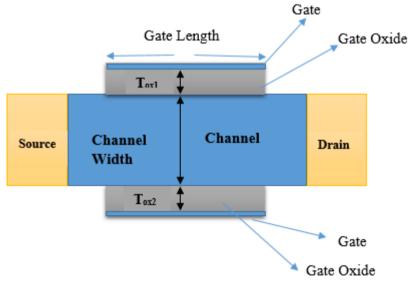

A 2-D image of the FinFET device structure used in the current simulation work is depicted in Fig. 1, which also specifies the various device parameters used for the simulation investigation.

Fig. 1. Two-Dimensional Double Gate FinFET [15]

## **2.2. Simulation Tool**

In this research study, a notable MuGFET tool from nanoHUB.org has been used to simulate the proposed device. MuGFET tool was developed and designed by Purdue University (USA). MuGFET can simulate with either PADRE or PROPHET, both of which were invented by Bell Laboratories. PROPHET is a partial differential equation profiler for one, two, or three dimensions, whereas PADRE is a device-oriented simulator for 2D or 3D devices with any shape. The software may generate valuable characteristic FET curves for engineers, particularly to thoroughly explain the fundamental physics of FETs. It can also provide self-consistent solutions to poison and drift-diffusion equations[16].

### 2.2.1. Simulation Design

The simulation tool is used to look into the characteristics of finFET using Ge and GaSb as channel materials. The output characteristic curves of the transistor are considered. The device is simulated and evaluated at 300K using the simulation parameters listed in Table 1.

| Gate Length                | 45nm                      |

|----------------------------|---------------------------|

| Channel width              | 10nm                      |

| Oxide thickness 1          | 2nm                       |

| Oxide thickness 2          | 2nm                       |

| Initial gate bias          | 0V                        |

| Final gate bias            | 1 <b>V</b>                |

| Initial drain bias         | 0.05V                     |

| Final drain bias           | 1 <b>V</b>                |

| Source extension length    | 50nm                      |

| Drain extension length     | 50nm                      |

| Final drain bias           | 1 <b>V</b>                |

| Band gap for GaSb          | 0.78 eV                   |

| Electron mobility for GaSb | 5000 cm <sup>2</sup> /V-S |

| Hole mobility for GaSb     | 1400 cm <sup>2</sup> /V-S |

| Electron affinity for GaSb | 4.06 eV                   |

## **Table 1. Simulation Parameters**

## **3. Results and Discussion**

This paper compares the results obtained for Ge and GaSb. Transconductance, drain current, threshold voltage, subthreshold swing, drain induced barrier lowering (DIBL) of Ge and GaSb are plotted on various figures. The results are obtained at various values of drain and gate voltages.

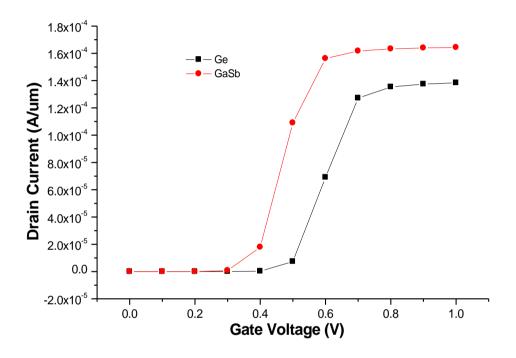

## **3.1.Gate Voltage Variation with Drain Current**

Fig. 2 illustrates a graph plotting the drain currents of Ge-finFET and GaSb-finFET for varying gate voltages. Current in GaSb increases as the gate voltage increases. This behavior is also reported in [15]. It is evident from the graph that GaSb-finFET exhibits higher on-current than the Ge-finFET at  $V_G = 1.0$  V. Higher on-current in FinFET devices can lead to improved performance, faster switching speeds, enhanced circuit speed, reduced propagation delay, improved power efficiency, better noise margins, and increased design flexibility. These implications make FinFETs desirable for high-performance and power-efficient applications in various fields, including microprocessors,

memory devices, and integrated circuits. It is worth noting that while on-current brings advantages, it also increases power dissipation and heat generation. Therefore, proper thermal management is crucial to ensure the device operates within acceptable temperature limits.

Higher on-current in FinFET devices can lead to improved performance, faster switching speeds, enhanced circuit speed, reduced propagation delay, improved power efficiency, better noise margins, and increased design flexibility. These implications make FinFETs desirable for high-performance and power-efficient applications in various fields, including microprocessors, memory devices, and integrated circuits. It is worth noting that while on-current brings advantages, it also increases power dissipation and heat generation. Therefore, proper thermal management is crucial to ensure the device operates within acceptable temperature limits.

Fig. 2. Gate Voltage Vs Drain Current

### **3.2.Drain Voltage Variation with Transconductance**

The transconductance,  $g_m$  quantifies the drain current variation with a gate-source voltage variation while keeping the drain- source voltage constant [15 -16]:

$$g_m = \frac{dI_D}{dV_{GS}} \tag{1}$$

where  $I_D$  is the drain current and  $V_{GS}$  is the gate-source voltage. Therefore, the value of gm is extracted by taking the derivative of the  $I_D$ - $V_{GS}$  curve.

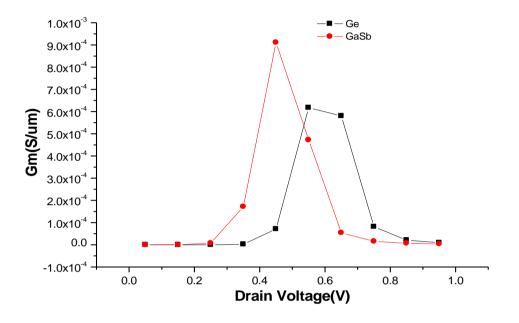

In Fig. 3, the variation of transconductance for Ge-finFET and GaSb-finFET with respect to drain voltage is presented. According to the graph, GaSb-finFET maintains a constant transconductance of 0 S/µm between drain voltages of 0.01V and 0.25V. The transconductance gradually increases with drain voltage and reaches a peak value of  $9.11 \times 10^{-4}$  S/µm at the drain voltage of 0.45 V. In contrast, the transconductance of Ge-finFET starts at 0 S/µm for drain voltages between 0V and 0.38V. It then increases until it reaches a maximum value of  $6.2 \times 10^{-4}$  S/µm at 0.55 V and then

declines at higher drain voltages. Comparing the two, GaSb-finFET has a highest transconductance as compared to Ge-finFET. Higher transconductance in FinFET devices offers advantages such as improved switching performance, higher drive currents, lower power consumption, enhanced noise immunity, and compact design. These benefits contribute to the continued advancement of semiconductor technology, enabling more efficient and powerful finFET devices.

Fig. 3. Drain Voltage Vs Transconductance

#### 3.3.Drain Voltage Versace Threshold Voltage.

Analyzing the threshold voltage of a device is of utmost importance when assessing its suitability as competent channel material for switching purposes [18]. The Threshold voltage is the minimum gate voltage required to set up a conduction path between the source and the drain[2]. The threshold voltage expression in case of a multi-gate field effect transistor (MuGFET) device structure can be expressed as [19]:

$$V_{th} = f_{ms} + 2f_f + \frac{Q_D}{C_{ox}} - \frac{Q_{SS}}{C_{ox}} + V_{in}$$

(2)

where  $Q_{SS}$  represents charge in the gate dielectric,  $C_{ox}$  is the gate capacitance,  $Q_D$  is the depletion charge in the channel,  $f_{ms}$  represents metal semiconductor work function difference between gate electrode and the semiconductor,  $f_f$  is the fermi potential.

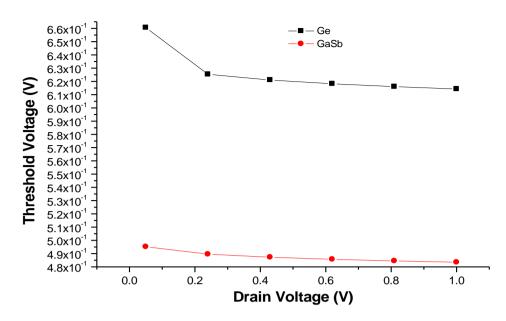

As shown in Fig. 4, the threshold voltage for GaSb-finFET is 0.48 V, whereas for Ge-finFET, it is 0.61 V at a drain voltage of 1 V. It is also observed that threshold voltage decreases as the drain voltage increases in both Ge and GaSb-finFETs. This lower threshold voltage for GaSb-finFET results in faster operation [10, 14]. Moreover, the lower threshold voltage aligns with the International Technology Roadmap for Semiconductors (ITRS) 2013 [3]. FinFET devices with a well-optimized threshold voltage can achieve lower power consumption. By carefully adjusting the threshold voltage, the leakage current can be minimized, leading to improved power efficiency. This is particularly important in modern electronic devices where power efficiency is a critical factor.

N. M. Shehu et al./ NIPES Journal of Science and Technology Research 5(2) 2023 pp. 322-330

Fig. 4. Drain Voltage Vs Threshold Voltage

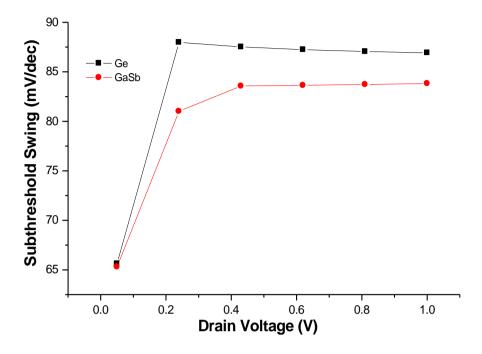

#### 3.4. Drain Voltage Variation with Subthreshold Swing

The subthreshold slope is the major parameter for calculating the leakage current. Furthermore, SS is calculated as in [16]:

$$SS(mV/dec) = \frac{dV_{GS}}{d(log_{10} I_{DS})}$$

(3)

Where  $V_{GS}$  is the gate-source voltage and  $I_{DS}$  is the drain-source current.

A typical value for the SS parameter of a MuGFET is 60 mV /decade, (i.e., a 60 mV change in gate voltage brings about a tenfold change in drain current) [17].

Fig. 5 shows a comparison of the subthreshold swing between Ge-finFET and GaSb-finFET. It is observed from Fig. 5 that Ge-finFET exhibits lowest subthreshold swing value of 65.6 mV/dec at a drain voltage of 0.05 V. Reduced subthreshold swing in FinFET devices lies in its ability to lower power consumption, improve energy efficiency, enhance performance, increase design flexibility, and enhance the scaling potential of transistors.

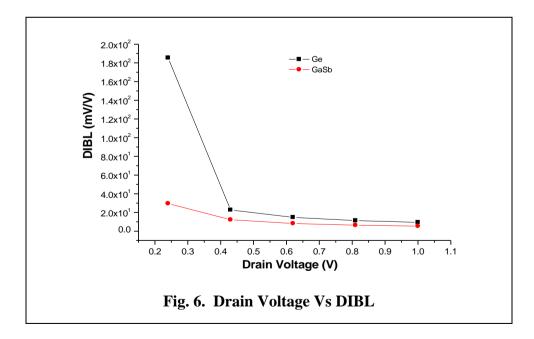

The DIBL is defined as the difference in threshold voltage when the drain voltage is increased from 0.01 V to 0.05 V [20]. Drain induced barrier lowering (DIBL) value can be calculated using the relation reported in [18 - 19]:

$$DIBL(\frac{mV}{V}) = \frac{\Delta V_{TH}}{\Delta V_{DS}}$$

(4)

where  $V_{TH}$  is the threshold voltage and  $V_{DS}$  is the drain-source voltage.

The drain induced barrier lowering (DIBL) for Ge-finFET and GaSb-finFET have been plotted with respect to drain voltage as shown in Fig. 6. GaSb-finFET produces the lowest DIBL value of 5.35 mV/V at the drain voltage of 1 V as compared to the Ge-finFET. Reduced DIBL offer several advantages in finFET devices. Firstly, it enhances the threshold voltage roll-off property, ensuring more stable device performance. Secondly, it allows for the proper maintenance of the device's operating frequency, enabling efficient and reliable operation. Lastly, it effectively minimizes the short channel effect (SCE), mitigating any undesired effects that can occur in shorter channel

lengths. Together, these benefits contribute to the overall optimization and improved functionality of the device [22]

Fig. 5. Drain Voltage Vs Subthreshold Swing

#### **3.5.Drain Voltage Variation with Drain Induced Barrier Lowering(DIBL)**

#### 4. Conclusion

This paper has presented a comprehensive analysis of the performance of two potential channel materials, Germanium (Ge) and Gallium Antimonide (GaSb), in finFETs. Through simulations

conducted in the Padre Simulator environment, critical factors such as short channel effects, transconductance, and on-current were evaluated. The results of the study demonstrate that the GaSb-finFET outperformed the Ge-finFET in both transconductance and on-current, while also exhibiting reduced short channel effects; DIBL and threshold Voltage roll-off. However, Ge-finFET exhibits better SS characteristics. These findings are of great significance for applications that require rapid switching capabilities and have the potential to drive further research and development in the field of semiconductor technology. Overall, the study highlights the importance of channel material selection in the design and optimization of finFETs and underscores the potential benefits of exploring alternative materials for electronic device development. The reliability and robustness of Ge and GaSb FinFET devices, which are emerging materials for advanced transistor technologies, are important aspects to consider in order to ensure their successful integration in various electronic applications. Future research efforts can be directed towards conducting comprehensive analyses of the long-term stability, aging effects, thermal behavior, and variability of these devices, which will provide valuable insights into their performance under prolonged operational conditions.

### References

- S. Verma, S. L. Tripathi, and M. Bassi, "Performance Analysis of FinFET device Using Qualitative Approach for Low-Power applications," *Proc. 3rd Int. Conf. 2019 Devices Integr. Circuit, DevIC 2019*, no. August, pp. 84–88, 2019, doi: 10.1109/DEVIC.2019.8783754.

- [2] S. Banerjee, E. Sarkar, and A. Mukherjee, "Effect of Fin Width and Fin Height on Threshold Voltage for Tripple Gate Rectangular FinFET," vol. 2, pp. 27–30, 2018.

- [3] A. F. Roslan *et al.*, "Comparative high-K material gate spacer impact in DG-finfet parameter variations between two structures," *Indones. J. Electr. Eng. Comput. Sci.*, vol. 14, no. 2, pp. 573–580, 2019, doi: 10.11591/ijeecs.v14.i2.pp573-580.

- [4] S. Mil and J. Palma, "FinFET with Constant Transconductance," vol. 1, no. 2, pp. 21–25, 2012, doi: 10.5923/j.msse.20120102.01.

- [5] M. Veshala, R. Jatooth, and K. R. Reddy, "Reduction of Short-Channel Effects in FinFET," *Int. J. Eng. Innov. Technol.*, vol. 2, no. 9, pp. 118–24, 2013.

- [6] S. L. Tripathi, R. A. Mishra, and R. A. Mishra, "Optimization of High Performance Bulk FinFET Structure Independent of Random Dopent Process Variations," *M icroelectronics Solid State Electron.*, vol. 2013, no. 2, pp. 29–38, 2013, doi: 10.5923/j.msse.20130202.03.

- [7] E. H. Minhaj, S. R. Esha, M. M. R. Adnan, and T. Dey, "Impact of Channel Length Reduction and Doping Variation on Multigate FinFETs," 2018 Int. Conf. Adv. Electr. Electron. Eng. ICAEEE 2018, pp. 1–4, 2019, doi: 10.1109/ICAEEE.2018.8642981.

- [8] A. Mahmood, W. A. Jabbar, Y. Hashim, and H. Bin Manap, "Effects of downscaling channel dimensions on electrical characteristics of InAs-FinFET transistor," *Int. J. Electr. Comput. Eng.*, vol. 9, no. 4, pp. 2902–2909, 2019, doi: 10.11591/ijece.v9i4.pp2902-2909.

- [9] E. Shang, Y. Ding, W. Chen, S. Hu, and S. Chen, "The Effect of Fin Structure in 5 nm FinFET Technology," *J. Microelectron. Manuf.*, vol. 2, no. 4, pp. 1–8, 2019, doi: 10.33079/jomm.19020405.

- [10] M. Kailasam and M. Govindasamy, "Impact of high-k gate dielectrics on short channel effects of dg n-finfet," *Int. J. Sci. Technol. Res.*, vol. 9, no. 3, pp. 2023–2026, 2020.

- [11] G. R. Murthy, S. Tiwari, and S. Marasu, "IMPACT OF DIELECTRIC MATERIALS ON FinFET CHARACTERISTICS AT 45nm USING SILVACO ATLAS 2-D SIMULATIONS," vol. 33, no. 1, pp. 61–64, 2021.

- [12] R. Prasher, D. Dass, and R. Vaid, "S TUDY OF N OVEL C HANNEL M ATERIALS USING III-V COMPOUNDS WITH VARIOUS G ATE D IELECTRICS," vol. 2, no. 1, 2013, doi: 10.5121/ijoe.2013.2102.

- [13] T. A. Bhat, M. Mustafa, and M. R. Beigh, "Study of short channel effects in n-FinFET structure for Si, GaAs, GaSb and GaN channel materials," *J. Nano- Electron. Phys.*, vol. 7, no. 3, pp. 1–5, 2015.

- [14] D. Jena, S. Das, A. Dastidar, and I. Engineering, "Performance comparison of GaN and Si FinFETs," vol. 9, no. 12, pp. 641–645, 2022.

- [15] S. I. et al. Shafiqul Islam et al., "A Comparative Study of Sub-10nm Si, Ge and GaAs n-Channel FinFET," *Int. J. Semicond. Sci. Technol.*, vol. 7, no. 1, pp. 1–6, 2017, doi: 10.24247/ijsstdec20171.

- [16] "Effect of High-k Gate Dielectric Materials on Electrical Characteristics of GaAs Channel Material Based Double Gate n-FinFET," vol. 9359, no. 8, pp. 51–56, 2016.

- [17] N. El, B. Hadri, and S. Patanè, "Effects of High-k Dielectric Materials on Electrical Characteristics of DG n-FinFETs," Int. J. Comput. Appl., vol. 139, no. 10, pp. 28–32, 2016, doi: 10.5120/ijca2016909385.

- [18] M. S. Islam, M. S. Hasan, M. R. Islam, A. Iskanderani, I. M. Mehedi, and M. T. Hasan, "Impact of Channel Thickness on the Performance of GaAs and GaSb DG-JLMOSFETs: An Atomistic Tight Binding based

N. M. Shehu et al./ NIPES Journal of Science and Technology Research 5(2) 2023 pp. 322-330

Evaluation," IEEE Access, vol. 9, pp. 117649-117659, 2021, doi: 10.1109/ACCESS.2021.3106141.

- [19] M. Mustafa, T. A. Bhat, and M. R. Beigh, "Threshold Voltage Sensitivity to Metal Gate Work-Function Based Performance Evaluation of Double-Gate n-FinFET Structures for LSTP Technology," *World J. Nano Sci. Eng.*, vol. 03, no. 01, pp. 17–22, 2013, doi: 10.4236/wjnse.2013.31003.

- [20] N. El, I. Boukortt, B. Hadri, A. Caddemi, G. Crupi, and S. Patan, "3-D Simulation of Nanoscale SOI n-FinFET at a Gate Length of 8 nm Using ATLAS SILVACO," vol. 16, no. 3, pp. 156–161, 2015.

- [21] P. Sahu, "Some Device Design Considerations to Enhance the Performance of DG- Some Device Design Considerations to Enhance the Performance of DG-MOSFETs," no. December 2014, 2013, doi: 10.4313/TEEM.2013.14.6.291.

- [22] A. S. C. & S. M. M. A. M. Md. Javed Hossain, "Impacts of Variations in Channel Length, Width and Gate Work Function of Gan FinFET and Si-FinFET on Essential Electrical Parameters," *Int. J. Electr. Electron. Eng. Res.*, vol. 9, no. 2, pp. 29–42, 2019, [Online]. Available: http://www.tjprc.org/publishpapers/2-15-1572850801-4.IJEEERDEC20194.pdf.